## Datapath Design Chapter 5 P & H

## Introduction

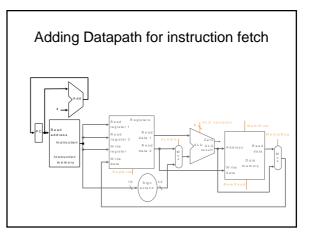

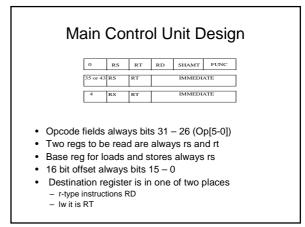

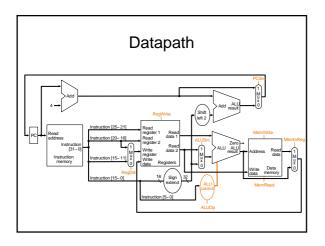

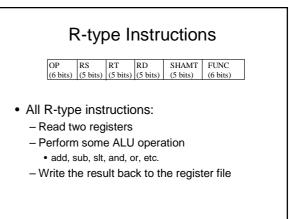

- Designing an implementation which contains subset of core MIPS instruction set:

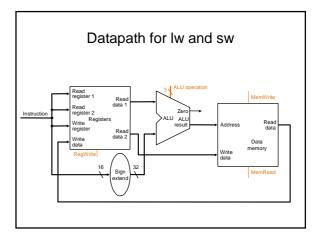

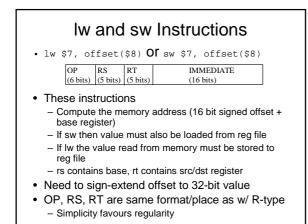

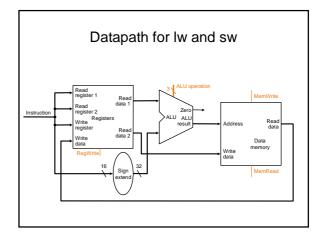

- Memory reference instructions (*Iw* & *sw*)

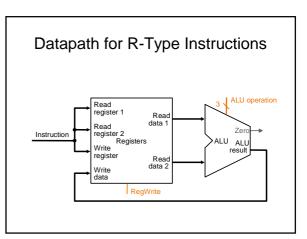

- Arithmetic-logic instructions (add, sub, and, or and slt)

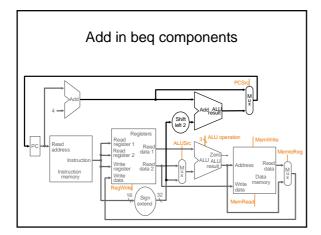

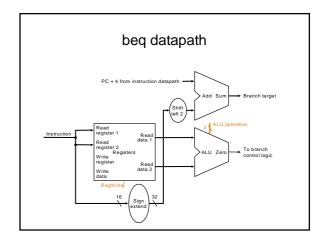

- Branch and jump instructions (beq, j)

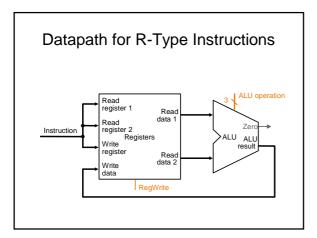

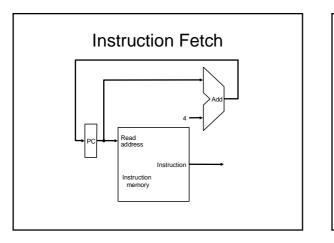

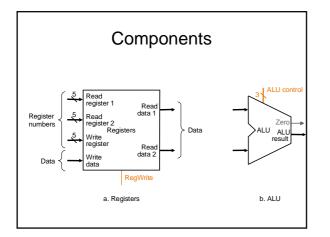

- Read 1 or 2 registers as specified in instruction

- Rest of steps dependent on instruction class

- Most will use ALU

- Many write value back to register file

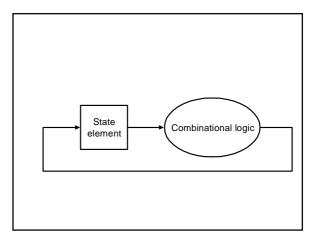

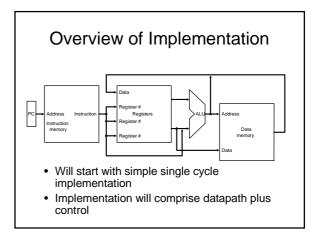

## Simple Implementation Scheme

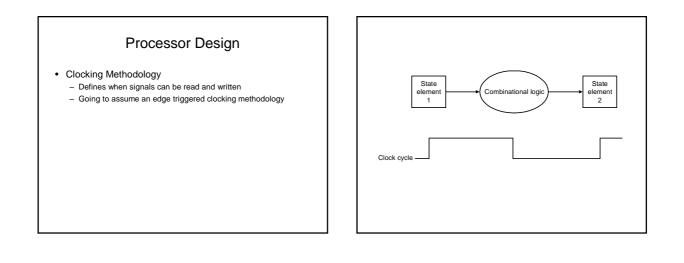

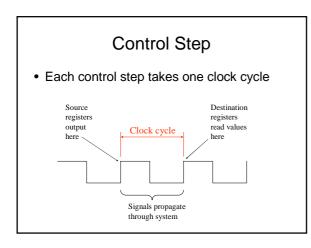

- All instructions execute in single clock cycle:

- No data path resource used more than once per clock cycle

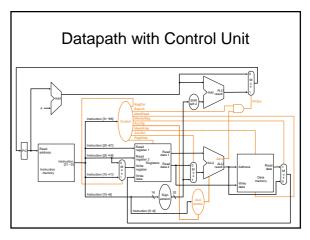

- Components of different instruction classes may be shared if no conflicts occur

- May require multiple connections to same input

- Multiplexer used to select appropriate input

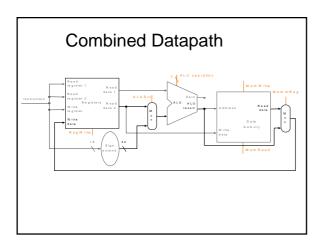

## Combining datapath for R-type and memory instructions

- Datapaths very similar

- Two main differences

- Second input to ALU is a register (for R-type) or sign-extended lower half of instruction (lw and sw)

- Value stored in dest register comes from ALU (R-type) or memory (lw)