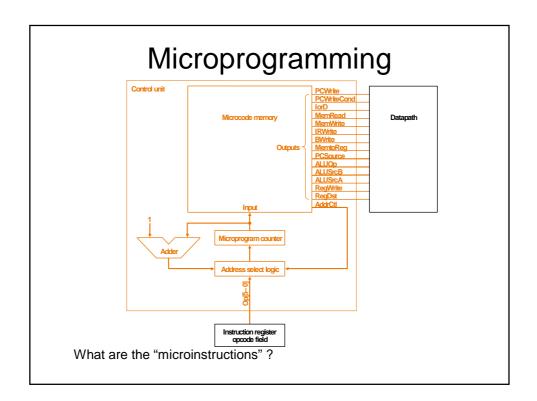

| <ul> <li>specii</li> </ul>                                                 | fication n     | netho | dolog   | У                   |           |                    |            |

|----------------------------------------------------------------------------|----------------|-------|---------|---------------------|-----------|--------------------|------------|

| - appr                                                                     | opriate if     | hundr | eds of  | opcodes,            | modes,    | cycles, etc.       |            |

|                                                                            | •              |       |         | •                   |           | •                  |            |

| <ul> <li>signals specified symbolically using microinstructions</li> </ul> |                |       |         |                     |           |                    |            |

| Label                                                                      | ALU<br>control | SRC1  | SRC2    | Register<br>control | Memory    | PCWrite<br>control | Sequencing |

| Fetch                                                                      | Add            | PC    | 4       |                     | Read PC   | ALU                | Seq        |

|                                                                            | Add            | PC    | Extshft | Read                |           |                    | Dispatch 1 |

| Mem1                                                                       | Add            | A     | Extend  |                     |           |                    | Dispatch 2 |

| LW2                                                                        |                |       |         |                     | Read ALU  |                    | Seq        |

|                                                                            |                |       |         | Write MDR           |           |                    | Fetch      |

| SW2                                                                        |                |       |         |                     | Write ALU |                    | Fetch      |

| Rformat1                                                                   | Func code      | A     | В       |                     |           |                    | Seq        |

|                                                                            |                |       |         | Write ALU           |           |                    | Fetch      |

|                                                                            | Cult           | A     | в       |                     |           | ALUOut-cond        | Fetch      |

| BEQ1                                                                       | Subt           | ~     | D       |                     |           |                    | 1 01011    |

| Microinstruction format              |              |                                          |                                                                                                                                 |  |  |  |

|--------------------------------------|--------------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Field name                           | Value        | Signals active                           | Comment                                                                                                                         |  |  |  |

|                                      | Add          | ALUOp = 00                               | Cause the ALU to add.                                                                                                           |  |  |  |

| ALU control                          | Subt         | ALUOp = 01                               | Cause the ALU to subtract; this implements the compare for<br>branches.                                                         |  |  |  |

|                                      | Func code    | ALUOp = 10                               | Use the instruction's function code to determine ALU control.                                                                   |  |  |  |

| SRC1<br>SRC2                         | PC           | ALUSrcA = 0                              | Use the PC as the first ALU input.                                                                                              |  |  |  |

|                                      | A            | ALUSrcA = 1                              | Register A is the first ALU input.                                                                                              |  |  |  |

|                                      | В            | ALUSrcB = 00                             | Register B is the second ALU input.                                                                                             |  |  |  |

|                                      | 4            | ALUSrcB = 01                             | Use 4 as the second ALU input.                                                                                                  |  |  |  |

|                                      | Extend       | ALUSrcB = 10                             | Use output of the sign extension unit as the second ALU input.                                                                  |  |  |  |

|                                      | Extshft      | ALUSrcB = 11                             | Use the output of the shift-by-two unit as the second ALU input.                                                                |  |  |  |

| Register<br>control<br>V<br>Memory F | Read         |                                          | Read two registers using the rs and rt fields of the IR as the register<br>numbers and putting the data into registers A and B. |  |  |  |

|                                      | Write ALU    | RegWrite,<br>RegDst = 1,<br>MemtoReg = 0 | Write a register using the rd field of the IR as the register number and<br>the contents of the ALUOut as the data.             |  |  |  |

|                                      | Write MDR    | RegWrite,<br>RegDst = 0,<br>MemtoReg = 1 | Write a register using the rt field of the IR as the register number and<br>the contents of the MDR as the data.                |  |  |  |

|                                      | Read PC      | MemRead,<br>lorD = 0                     | Read memory using the PC as address; write result into IR (and the MDR).                                                        |  |  |  |

|                                      | Read ALU     | MemRead,<br>lorD = 1                     | Read memory using the ALUOut as address; write result into MDR.                                                                 |  |  |  |

|                                      | Write ALU    | MemWrite,<br>lorD = 1                    | Write memory using the ALUOut as address, contents of B as the<br>data.                                                         |  |  |  |

| PC write control                     | ALU          | PCSource = 00<br>PCWrite                 | Write the output of the ALU into the PC.                                                                                        |  |  |  |

|                                      | ALUOut-cond  | PCSource = 01,<br>PCWriteCond            | If the Zero output of the ALU is active, write the PC with the contents<br>of the register ALUOut.                              |  |  |  |

|                                      | jump address | PCSource = 10,<br>PCWrite                | Write the PC with the jump address from the instruction.                                                                        |  |  |  |

| Sequencing                           | Seq          | AddrCtl = 11                             | Choose the next microinstruction sequentially.                                                                                  |  |  |  |

|                                      | Fetch        | AddrCtl = 00                             | Go to the first microinstruction to begin a new instruction.                                                                    |  |  |  |

|                                      | Dispatch 1   | AddrCtl = 01                             | Dispatch using the ROM 1.                                                                                                       |  |  |  |

|                                      | Dispatch 2   | AddrCtl = 10                             | Dispatch using the ROM 2.                                                                                                       |  |  |  |

## Maximally vs. Minimally Encoded

- No encoding:

- 1 bit for each datapath operation

- faster, requires more memory (logic)

- used for Vax 780 an astonishing 400K of memory!

- Lots of encoding:

- send the microinstructions through logic to get control signals

- uses less memory, slower

- Historical context of CISC:

- Too much logic to put on a single chip with everything else

- Use a ROM (or even RAM) to hold the microcode

- It's easy to add new instructions

## Microcode: Trade-offs

- Distinction between specification and implementation is sometimes blurred

- Specification Advantages:

- Easy to design and write

- Design architecture and microcode in parallel

- Implementation (off-chip ROM) Advantages

- Easy to change since values are in memory

- Can emulate other architectures

- Can make use of internal registers

- Implementation Disadvantages, SLOWER now that:

- Control is implemented on same chip as processor

- ROM is no longer faster than RAM

- No need to go back and make changes