## MESI

• What happens if a core has an Invalid entry but tries to access it ?

....

....

....

- The cache with the Modified entry needs to write the entry back to memory and become a Shared entry

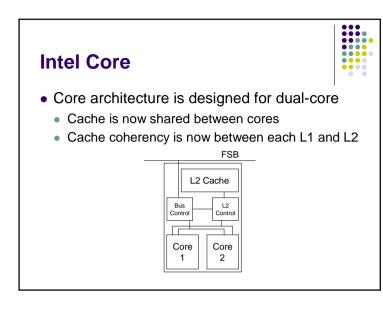

- This means an Intel Pentium D has to involve the FSB in all of it's cache coherency updates even though they are on the same die

....

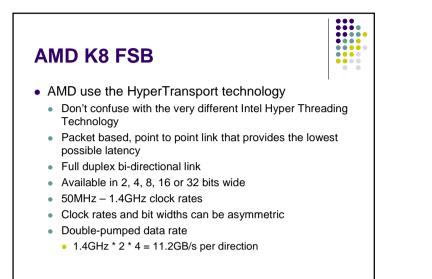

## Athlon 64 FSB

• The Athlon 64 has a single HyperTransport link to connect to I/O subsystem

....

- 16bit, bi-directional, DDR at 800MHz (754) or 1GHz (939)

- 2 \* 2 \* 2 \* 1000 = 8GB/s

- Can have either a single chip solution or stay with two chip, northbridge, southbridge combination

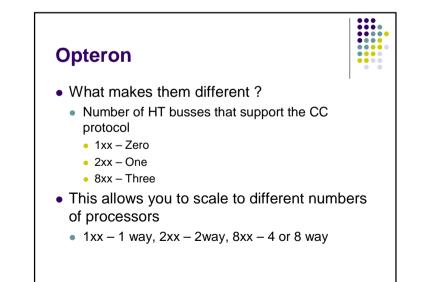

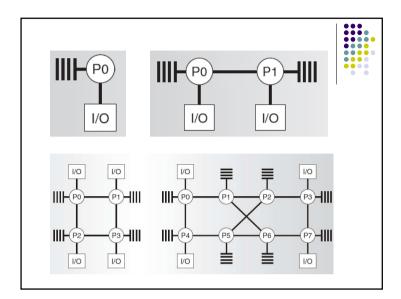

## Opteron

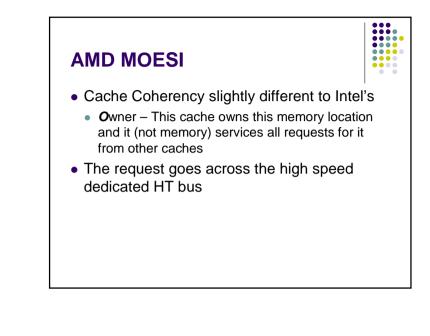

- Uses HT for both the I/O interconnect and CPU interconnect

- CPU interconnect requires an additional Cache Coherency protocol addition to HT

- Come in three variants

- 1xx Memory controller and 3 HT links

- 2xx Memory controller and 3 HT links

- 8xx Memory controller and 3 HT links

....

....

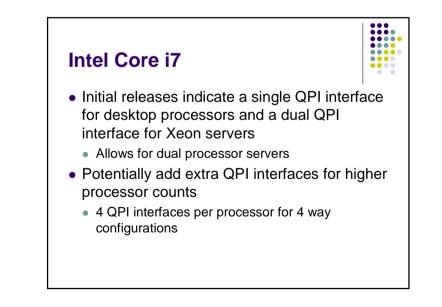

## **Quick Path**

- Point to Point serial, full duplex

- Width and clock speed can be altered depending on the application

- Core i7 will release with 12.8GB/s each direction

- 20bits ("lanes") wide (16data + 4 checksum)

- 3.2GHz DDR clock

- Lanes can be reduced dynamically for power saving